User:John R. Brews/Draft: Difference between revisions

Jump to navigation

Jump to search

imported>John R. Brews (→Traps) |

imported>John R. Brews (Replacing page with '{{Image|MOS Capacitor.PNG|right|250px|Cross section of MOS capacitor showing charge layers}} {{TOC|right}} ==Schottky diode== ==Notes== <references/>') |

||

| Line 1: | Line 1: | ||

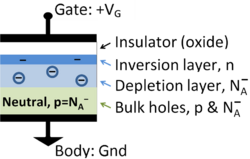

{{Image|MOS Capacitor.PNG|right|250px|Cross section of MOS capacitor showing charge layers}} | {{Image|MOS Capacitor.PNG|right|250px|Cross section of MOS capacitor showing charge layers}} | ||

{{TOC|right}} | {{TOC|right}} | ||

== | ==Schottky diode== | ||

==Notes== | ==Notes== | ||

<references/> | <references/> | ||